## A New Decoder-type Gate Driver Circuit for High Resolution

Jae-Hee Jo<sup>1</sup>, and Seung-Woo Lee<sup>1</sup>

<sup>1</sup>Dept. of Inform. Display, Your College, Town/City, Seoul 121-791, Korea

Tel.:82-2-961-0971, E-mail: seungwoolee@khu.ac.kr

These days, the display has various form factors which are flexible, foldable, and stretchable [1]. Due to the physical stress, the reliability of the gate driver circuit should be considered. However, the fault of one stage is fatal in the conventional shift register-type gate driver circuit, because it causes a malfunction in the whole subsequent stages. To solve this problem, decoder-type gate driver circuits had been proposed [2]. Because each stage operates independently, the effect of fault can be minimized. However, unlike the conventional gate driver, the number of signals of the decoder-type gate driver should be increased according to the resolution of the display. Thus it is difficult to apply to high resolution like FHD and 4k UHD.

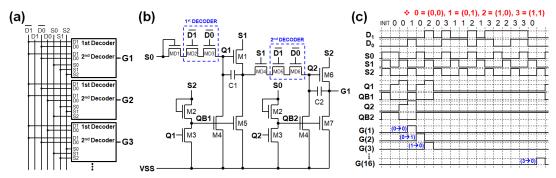

Fig. 1. (a) Block diagram, (b) circuit diagram of unit stage and (c) timing diagram of proposed gate driver.

To overcome this problem, we propose a new decoder-type gate driver as shown in Fig. 1. The unit stage of the proposed circuit consists of two decoding stages. Instead of using different decoder signals in two decoding stages, we use the same decoder signals which are distinguished by the timing. The input signal is transmitted to the next stage only when the decoder is open at the same timing of the input signal. Thus gate voltage is only output when the 1<sup>st</sup> and 2<sup>nd</sup> decoder stage sequentially operates. Moreover, the gate output voltage has no blank timing by using the same decoder signal between the 2<sup>nd</sup> decoding stage of the previous stage and the 1<sup>st</sup> decoding stage of the next stage.

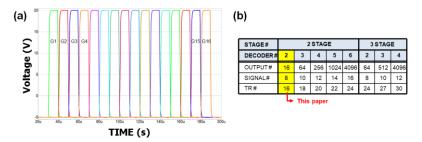

Fig. 2. (a) Simulation results and (b) comparison according to number of decoder signals and stages.

Fig. 2(a) shows simulation results of 16 stage of proposed gate driver. And as shown in Fig. 2(b), proposed circuit use 16 signals and 24 transistors to drive FHD resolution while conventional decoder-type gate driver uses 23 signals and 21 transisotrs [2].

## Acknowledgment

This work was supported in part by the Brain Korea 21 (BK21) Plus Program (Future-Oriented Innovative Brain Raising Type) through the National Research Foundation of Korea (NRF) under Grant 21A20130000018, in part by Electronics and Telecommunications Research Institute (ETRI) grant funded by the Korea government (Development of Creative Technology for ICT) under Grant 20ZB1100, and in part by the IC Design Education Center (IDEC), Korea.

## References

- 1. J.-H. Hong et al., J. Soc. Inf. Display, 25(3), 194 (2017).

- 2. J. Kim et al., IEEE Transactions on Electron Devices, 65(8), 3269 (2018).